Viewer#

Important

This is an experimental tool that is currently under development

The MemryX viewer provides a GUI interface to various SDK tools. This includes the Neural Compile, the Simulator, and the Chip Programmer.

Usage#

To run the viewer you need to run the following command.

mx_viewer

Note

If the GUI fails to start, you may need to install a Qt5 library. On Debian/Ubuntu, you can use sudo apt install libqt5x11extras5, then try the GUI again.

Compiler#

The compiler tab offers a visual interface to the MemryX neural compiler. It provides basic compiler functionality using a few simple steps.

1. Select the neural network models

2. Select the target system

(Optional) Select the target performance

3. Compile, by clicking the “start” button

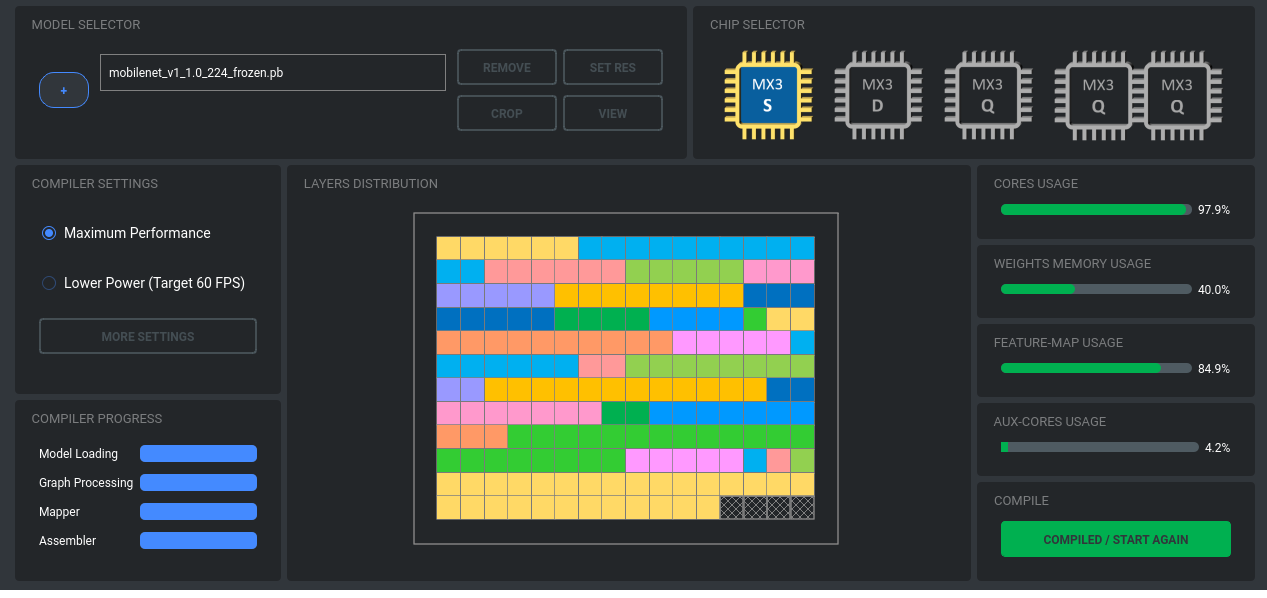

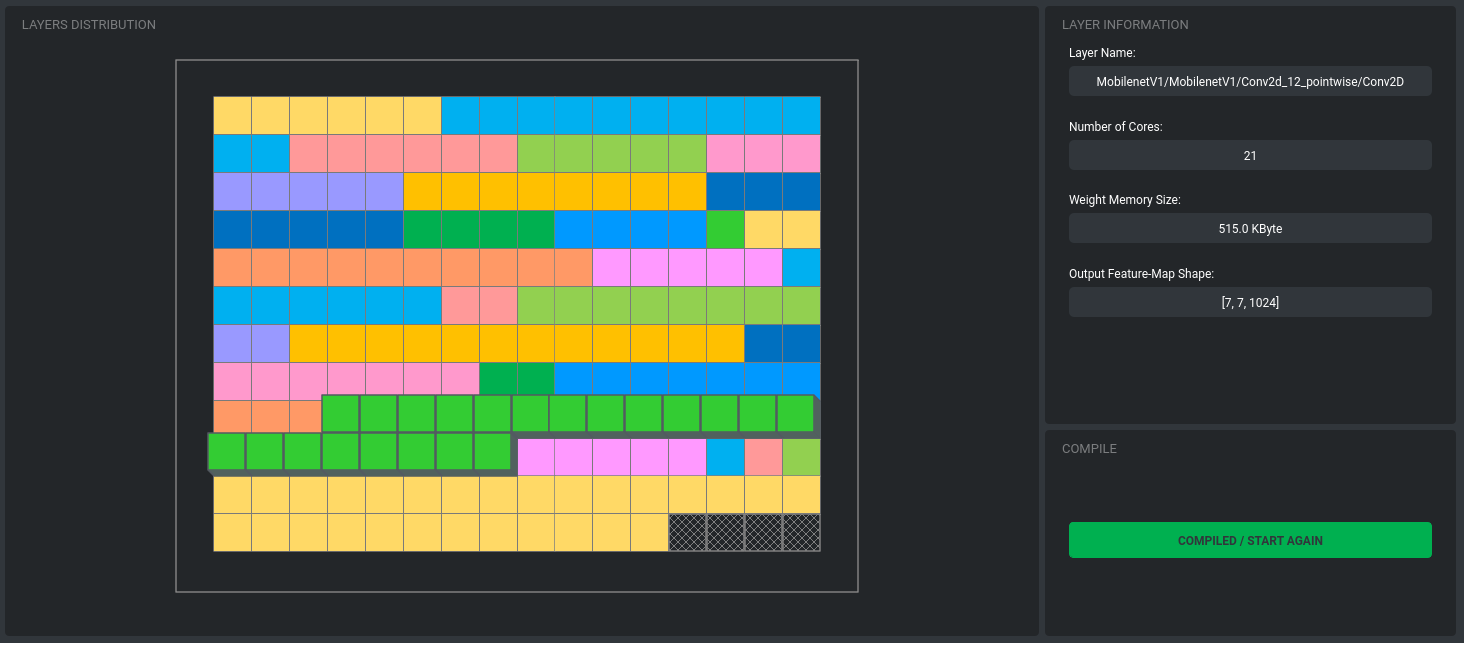

The following figure shows the final result after compiling a MobileNet model to a single chip MX3 system. The compiler will also generate the DFP needed to program the accelerator or run the simulator.

The compiler will show the utilization percentage of the various accelerator resources. The layer distribution view shows how many cores are assigned to each neural network layer. By selecting a cluster of cores additional details including layer mapped to the cores, weight memory assigned to the layer etc. can be obtained. This feature has been demonstrated in the following figure.

Simulator#

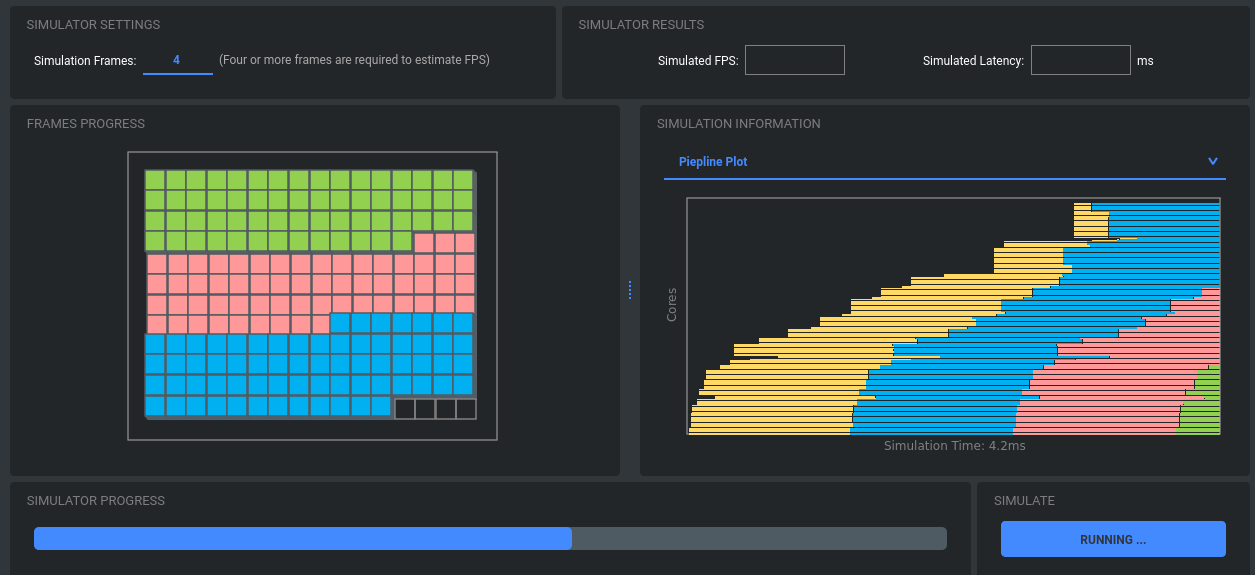

The second tab is the simulator one. It offers a simple interface to the basic simulator features. The user need to select the number of frames they need to simulate and start the simulation.

During the simulation, the program previews how data flows through the cores and chips, where it colors each new frame differently.

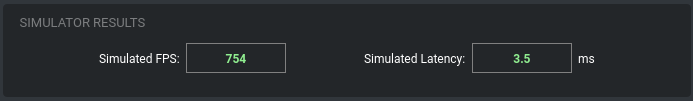

Finally, the simulated FPS and latency will get reported to the user.

Accelerator#

The third tab allows the user to program the chip using the compiled DFP and easily perform inference on the connected MXA and get latency and FPS.